# **Data Sheet**

# AR2112 Multi-Mode, Radio-on-a-Chip for IEEE 802.11b/g Wireless LANs

### **General Description**

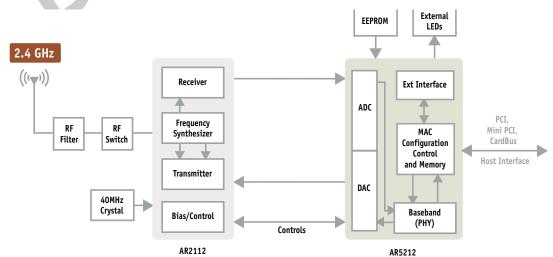

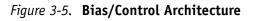

The Atheros AR2112 iMs part of the two-chip AR5002G and AR5002AP-G solutions for IEEE 802.11b/g (2.4 GHz) wireless local area networks (WLANs). When combined with the AR5212 or AR2312, these chip sets enable a high performance, low cost, compact solution that easily fits onto one side of a PC Card, Mini PCI Card, or access point applications.

The AR2112 operates in the 2.4 GHz frequency bands:

| Freq    | Bands | Frequency                      |

|---------|-------|--------------------------------|

| 2.4 GHz |       | 2.312 – 2.472 GHz<br>2.484 GHz |

The transmitter combines baseband in-phase (I) and quadrature (Q) signals, up-converts them to the desired frequency channel, and drives the RF signal off-chip through the integrated power amplifier.

The receiver uses an integrated dual conversion architecture and requires no off-chip intermediate frequency (IF) filters.

The frequency synthesizer operates with 5 MHz steps to match the frequency channels

defined by IEEE 802.11b/g as well as supporting the Atheros Super G<sup>TM</sup> mode. An on-chip crystal oscillator allows clock generation with a single external crystal configuration.

The transmitter, receiver, and frequency synthesizer functions are controlled using the AR5212 or AR2312 through a serial programming bus and on-chip control registers.

All internal bias currents are generated on-chip with a single external reference resistor.page

#### Features

- Radio chip for the Atheros IEEE 802.11b/g radio

- No external VCOs and SAW filters needed

- 64-pin leadless plastic chip carrier package

- Together with the AR5212 MAC/Baseband processor, or the AR2312 Wireless Systemon-a-Chip (WiSoC):

- IEEE 802.11b/g compatible

- Low power operating and sleep mode

© 2000-2003 Atheros Communications, Inc. All rights reserved. Atheros™, 5-UP™, Driving the Wireless Future™, Atheros Driven™, Atheros Turbo Mode™, and the Air is Cleaner at 5-GHz™ are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders.

# AR5002G System Block Diagram

Subject to change without notice.

## 1. Pin Descriptions

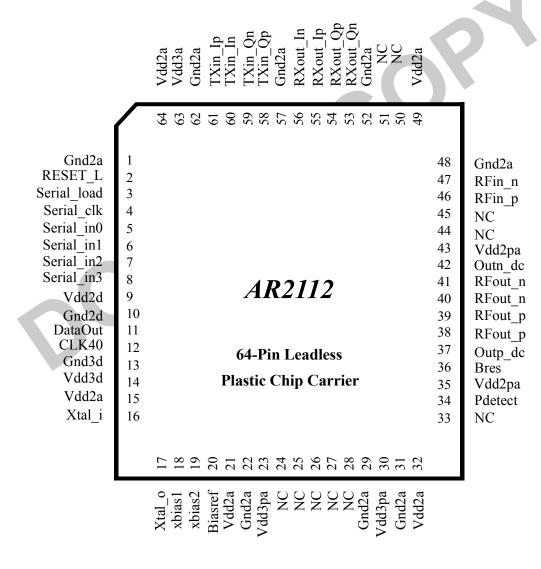

This section contains a package pinout and a tabular listing of the signal descriptions.

The following nomenclature is used for signal names:

- NC indicates no connection should be made to this pin. See Table 1-1 for details.

- \_L at the end of the signal name indicates active low signals.

- p at the end of the signal indicates the positive side of a differential signal.

- n at the end of the signal indicates the negative side of a differential signal.

The following nomenclature is used for signal types described in Table 1-1:

- IA indicates an analog input.

- I indicates a digital input.

- OA indicates an analog output.

- O indicates a digital output.

- P indicates a power/ground.

Figure 1-1. Package Pinout (Top View)

| Symbol      | Pin    | Туре | Source or<br>Destination | Description                                                                  |

|-------------|--------|------|--------------------------|------------------------------------------------------------------------------|

| Receiver    |        |      |                          |                                                                              |

| RFin_n      | 47     | IA   | RF input                 | Differential RF inputs at 2.4 GHz. Use one side for single-ended             |

| RFin_p      | 46     | IA   | RF input                 | input.                                                                       |

| RXout_Qn    | 53     | OA   | BB/WiSoC                 | Differential baseband I and Q outputs from the receiver to the               |

| RXout_Qp    | 54     | OA   | BB/WiSoC                 | MAC/Baseband processor or the WiSoC. Anti-aliasing filter is on-chip.        |

| RXout_In    | 56     | OA   | BB/WiSoC                 |                                                                              |

| RXout_Ip    | 55     | OA   | BB/WiSoC                 |                                                                              |

| Transmitter |        |      |                          |                                                                              |

| TXin_Qn     | 59     | IA   | BB/WiSoC                 | Differential baseband I and Q inputs from DAC on the MAC/                    |

| TXin_Qp     | 58     | IA   | BB/WiSoC                 | Baseband processor or the WiSoC. Reconstruction filter is on-chip.           |

| TXin_In     | 60     | IA   | BB/WiSoC                 |                                                                              |

| TXin_Ip     | 61     | IA   | BB/WiSoC                 |                                                                              |

| RFout_n     | 41, 40 | OA   | RF output                | Differential 2.4 GHz RF power amplifier outputs.                             |

| RFout_p     | 39, 38 | OA   | RF output                |                                                                              |

| Pdetect     | 34     | Ι    | —                        | External Envelope Detector Input for 2.4 GHz RF signal.                      |

| Outp_dc     | 37     | Ι    | Analog                   | 2.4 GHz PA drain bias. 3.3 V bias.                                           |

| Outn_dc     | 42     | Ι    | Analog                   |                                                                              |

| Vdd2pa      | 43, 35 | Ι    | Analog 2.5 V             | PA Vdd for the 2.4 GHz PA.                                                   |

| Vdd3pa      | 23, 30 | Ι    | Analog 3.3 V             | PA Vdd for the 2.4 GHz PA driver.                                            |

| Bres        | 36     | Ι    |                          | 3 k $\Omega$ Bias resistor to Vdd2a for 2.4 GHz PA                           |

| Bias/Contro | L      |      |                          |                                                                              |

| Xtal_i      | 16     | Ι    | 40 MHz                   | Crystal input and output.                                                    |

|             |        |      | crystal                  |                                                                              |

| Xtal_o      | 17     | 0    | 40 MHz<br>crystal        |                                                                              |

| CLK40       | 12     | 0    | BB/WiSoC                 | 40 MHz reference clock. 3.3 V.                                               |

| RESET_L     | 2      | Ι    | BB/WiSoC                 | Active low reset. Must be active for at least 500 ns., 3.3 V.                |

| Serial_load | 3      | Ι    | BB/WiSoC                 | Load for control shift register. 3.3 V.                                      |

| Serial_clk  | 4      | Ι    | BB/WiSoC                 | Shift clock for control shift register. 3.3 V.                               |

| Serial_in0  | 5      | Ι    | BB/WiSoC                 | Input data for control shift register. 3.3 V.                                |

| Serial_in1  | 6      | Ι    | BB/WiSoC                 | Input data for control shift register. 3.3 V.                                |

| Serial_in2  | 7      | Ι    | BB/WiSoC                 | Input data for control shift register. 3.3 V.                                |

| Serial_in3  | 8      | Ι    | BB/WiSoC                 | Input data for control shift register. 3.3 V.                                |

| DataOut     | 11     | 0    | BB/WiSoC                 | Digital Data Output Pin.                                                     |

| Biasref     | 20     | Ι    | 6.19 kΩ                  | Reference pin for external bias resistor. 6.19 k $\Omega \pm 1\%$ to ground. |

Table 1-1. Signal to Pin Relationships and Descriptions

| Symbol   | Pin                                    | Туре | Source or<br>Destination | Description                                    |

|----------|----------------------------------------|------|--------------------------|------------------------------------------------|

| xbias1   | 18                                     | OA   | Bias Output              | General purpose analog bias pins.              |

| xbias2   | 19                                     | OA   | Bias Output              |                                                |

| Power    |                                        |      |                          |                                                |

| Vdd3a    | 63                                     | Р    | 3.3 V                    | Analog 3.3 V power supply for Synthesizer VCO. |

| Vdd2a    | 15, 21,<br>32, 49,<br>64               | Р    | 2.5 V                    | Analog 2.5 V power supply.                     |

| Vdd3d    | 14                                     | Р    | 3.3 V                    | Digital Vdd for 3.3 V pads.                    |

| Vdd2d    | 9                                      | Р    | 2.5 V                    | Digital 2.5 V Vdd for logic.                   |

| Gnd2a    | 1, 22,<br>29, 31,<br>48, 52,<br>57, 62 | Р    | 0 V                      | Analog ground.                                 |

| Gnd2d    | 10                                     | Р    | 0 V                      | Digital ground for logic.                      |

| Gnd3d    | 13                                     | Р    | 0 V                      | Digital I/O ground.                            |

| Reserved |                                        |      |                          |                                                |

| NC       | 24-28,<br>33, 44-<br>45, 50-<br>51     | I/O  | -                        | Do Not Connect                                 |

|          | 5                                      |      |                          |                                                |

#### Table 1-1. Signal to Pin Relationships and Descriptions (continued)

## 2. Electrical Characteristics

#### 2.1 Absolute Maximum Ratings

Table 2-1 summarizes the absolute maximum ratings and Table 2-2 lists the recommended operating conditions for the AR2112. Absolute maximum ratings are those values beyond which damage to the device can occur. Functional operation under these conditions, or at any other condition beyond those indicated in the operational sections of this document, is not recommended.

| Symbol             | Parameter                                    | Max. Rating | Unit |

|--------------------|----------------------------------------------|-------------|------|

| V <sub>dd2</sub>   | Supply voltage                               | -0.3 to 3.0 | V    |

| V <sub>dd3</sub>   | Maximum I/O supply voltage                   | -0.3 to 4.0 | V    |

| RF <sub>in</sub>   | Maximum RF input (reference to 50 $\Omega$ ) | +10         | dBm  |

| T <sub>store</sub> | Storage temperature                          | -65 to 150  | °C   |

| ESD                | Electrostatic discharge tolerance            | 1500        | V    |

#### Table 2-1. Absolute Maximum Ratings

#### 2.2 Recommended Operating Conditions

#### Table 2-2. Recommended Operating Conditions

| Symbol            | Parameter            | Conditions       | Min.  | Тур. | Max.  | Unit |

|-------------------|----------------------|------------------|-------|------|-------|------|

| V <sub>dd2</sub>  | Supply voltage       | $\pm 5\%^{[1]}$  | 2.375 | 2.5  | 2.625 | V    |

| V <sub>dd3</sub>  | I/O voltage          | $\pm 10\%^{[1]}$ | 3.0   | 3.3  | 3.6   | V    |

| T <sub>case</sub> | Case temperature     | —                | 0     | 25   | 95    | °C   |

| Tj                | Junction temperature | —                | 0     | 50   | 110   | °C   |

[1]The recommended power-on sequence is to have  $V_{dd3}$  lag  $V_{dd2}.$

#### 2.3 AC Electrical Characteristics

The following conditions apply to all characteristics unless otherwise specified:  $V_{dd2} = 2.5 \text{ V}$ ,  $V_{dd3} = 3.3 \text{ V}$ ,  $T_{case} = 25 \text{ °C}$ .

Unless otherwise specified, all measurements are to be performed with test circuits based on the reference design.

#### 2.3.1 Receiver Characteristics

Table 2-3 summarizes the receivercharacteristics for the AR2112.

| Symbol                  | Parameter                                                                   | Conditions                              | Min.           | Тур.                     | Max.       | Unit   |

|-------------------------|-----------------------------------------------------------------------------|-----------------------------------------|----------------|--------------------------|------------|--------|

| F <sub>rx</sub>         | Receive input frequency range                                               | 5 MHz center frequency                  | 2.312          |                          | 2.484      | GHz    |

| NF                      | Receive chain noise figure                                                  | See Note <sup>[1]</sup>                 | 7              | 5.5                      | _          | dB     |

| S <sub>rf</sub>         | Sensitivity<br>CCK, 1 Mbps<br>CCK, 11 Mbps<br>OFDM, 6 Mbps<br>OFDM, 54 Mbps | See Note <sup>[2]</sup>                 |                | -95<br>-90<br>-92<br>-73 |            | dBm    |

| IP1dB                   | Input 1 dB compression (min. gain)                                          | _                                       | -12            | -10                      | _          | dBm    |

| IIP3                    | Input 3rd intercept point (min.<br>gain)                                    | -                                       | -3             | -1                       | —          | dBm    |

| Z <sub>RFin_input</sub> | Recommended LNA differential drive impedance                                | See Note <sup>[3]</sup>                 | _              | 9+j40                    | —          | _      |

| ER <sub>phase</sub>     | I,Q phase error                                                             |                                         | _              | 1.5                      | 2          | degree |

| ERamp                   | I,Q amplitude error                                                         |                                         |                | 0.5                      | 1          | dB     |

| R <sub>adj</sub>        | Adjacent channel rejection<br>CCK<br>OFDM, 6 Mbps<br>OFDM, 54 Mbps          | 10 to 20 MHz<br>See Note <sup>[4]</sup> | 35<br>16<br>-1 | 24<br>7                  |            | dB     |

| BB <sub>atten</sub>     | Baseband filter attenuation<br>20 MHz offset<br>40 MHz offset               |                                         |                | -21<br>-46               | -17<br>-40 | dB     |

| BB <sub>ripple</sub>    | Baseband filter passband ripple                                             | _                                       | —              | 0.4                      | 1          | dB     |

| TRpowup                 | Time for power up (from synth on)                                           | _                                       | _              | 1                        | _          | μs     |

#### Table 2-3. Receiver Characteristics for 2.4 GHz operation

[1]Measured using the balun recommended by Atheros. An increase of 2 dB in noise figure is expected at 85°C. The use of an external LNA is recommended.

[2]Sensitivity performance is based on the Atheros reference design which includes RF filter, TX/RX antenna switch and an external LNA.

[3]Refer to the hardware design guide for information.

[4] Measured with AR5212.

#### 2.3.2 Transmitter Characteristics

Table 2-4 summarizes the transmittercharacteristics for the AR2112.

| Symbol                  | Parameter                                             | Conditions                                          | Min.       | Тур.       | Max.     | Unit |

|-------------------------|-------------------------------------------------------|-----------------------------------------------------|------------|------------|----------|------|

| F <sub>tx</sub>         | Transmit output frequency range                       | 5 MHz center<br>frequency                           | 2.312      | —          | 2.484    | GHz  |

| P <sub>out</sub>        | Mask Compliant CCK output power                       | T <sub>amb</sub> = 25 °C<br>See Note <sup>[1]</sup> | _          | 10         |          | dBm  |

|                         | EVM Compliant OFDM output power for 64QAM             |                                                     |            | 6          |          | dBm  |

| SPgain                  | PA gain step                                          | See Note <sup>[2]</sup>                             | —          | 0.5        | -        | dB   |

| A <sub>pl</sub>         | Accuracy of power leveling loop                       | See Note <sup>[3]</sup>                             | -          | ± 0.5      | ± 1.5    | dB   |

| Z <sub>RFout_load</sub> | Recommended PA differential load impedance            | See Note <sup>[4]</sup>                             | -          | 20 - j10   | -        | —    |

| OP1dB                   | Output P1dB (max. gain) See note 3                    | 2.442 GHz, 25 °C                                    | 13         | 15         | —        | dBm  |

| OIP3                    | Output 3rd order intercept point (max. gain)          | 2.442 GHz, 25 °C                                    | 24         | 26         | _        | dBm  |

| SS                      | Sideband suppression                                  |                                                     | _          | -50        | -30      | dBc  |

| C <sub>leak</sub>       | Carrier leakage                                       |                                                     | _          | -35        | -23      | dBc  |

| LO <sub>Harm</sub>      | LO Harmonics<br>Center frequencies: 2.412 - 2.472 GHz | -                                                   |            |            |          | dBc  |

|                         | 2.016 GHz<br>2.688 GHz                                |                                                     | _          | 55<br>55   |          |      |

|                         | Center frequency: 2,484 GHz<br>2.112 GHz<br>2.816 GHz |                                                     | _          | 45<br>50   |          |      |

| RS                      | Synthesizer reference spur:                           | —                                                   | _          | -55        |          | dBc  |

| Tx <sub>mask</sub>      | Transmit spectral mask                                |                                                     |            |            |          | dBr  |

|                         | ССК                                                   | At 11 MHz offset<br>At 22 MHz offset                | -30<br>-50 | -35<br>-53 | _        |      |

|                         | OFDM                                                  | At 11 MHz offset<br>At 20 MHz offset                | -20<br>-28 | -27<br>-38 | _        |      |

|                         |                                                       | At 30MHz offset                                     | -51        | -52        | <u> </u> |      |

| TTpowup                 | Time for power up (from synth on)                     | —                                                   |            | 1.5        | —        | μs   |

| Table 2-4. | Transmitter | Characteristics | for 2.4 | GHz operati | ion      |

|------------|-------------|-----------------|---------|-------------|----------|

| 1001C L 1. |             | characteristics |         | one operati | <b>v</b> |

[1]Measured using the balun recommended by Atheros under closed-loop power control. The use of an external PA with external power detector is recommended. See application notes on *External Power Control for Design Using* AR5002.

[2]Guaranteed by design.

[3]Manufacturing calibration required.

[4]Refer to the design guide for information.

#### 2.3.3 Synthesizer Characteristics

Table 2-5 summarizes the synthesizer characteristics for the AR2112.

| Symbol            | Parameter                      | Conditions                                                         | Min.  | Тур. | Max.  | Unit   |

|-------------------|--------------------------------|--------------------------------------------------------------------|-------|------|-------|--------|

| Pn                | Phase noise (at Tx_Out)        | 30 kHz offset                                                      | —     | -105 | -100  | dBc/Hz |

|                   |                                | 100 kHz offset                                                     | —     | -105 | -100  | dBc/Hz |

|                   |                                | 500 kHz offset                                                     | _     | -105 | -100  | dBc/Hz |

|                   |                                | 1 MHz offset                                                       | _     | -108 | -103  | dBc/Hz |

| F <sub>c</sub>    | Center channel frequency       | Center frequency<br>at 5 MHz spacing<br>(see Note <sup>[1]</sup> ) | 2.312 | -    | 2.484 | GHz    |

| F <sub>ref</sub>  | Reference oscillator frequency | ± 25 ppm                                                           | _     | 40   |       | MHz    |

| F <sub>step</sub> | Frequency step size (at RF)    | See Note <sup>[2]</sup>                                            | -     | 5    | _     | MHz    |

| TSpowup           | Time for power up (from sleep) | -                                                                  | F     | 0.2  | —     | ms     |

#### Table 2-5. Synthesizer Composite Characteristics

[1]Frequency is measured at the TX output.

C

[2]5 MHz channel spacing is for the 2.312 to 2.472 GHz band. 2.484 GHz is for use in Japan.

#### 2.3.4 Power Consumption Parameters

The following conditions apply to the typical characteristics unless otherwise specified:

$V_{dd2}$  = 2.5 V,  $V_{dd3}$  = 3.3 V,  $T_{amb}$  = 25  $^{\circ}C$

Table 2-6 shows the typical power drain on each of the four on-chip power supply domains as a function of the AR2112's operating mode.

| Table 2-6. | Power Consum  | ption for 2.4 | GHz Operation   | (All in milliWatts) |

|------------|---------------|---------------|-----------------|---------------------|

| 10010 2 0. | i ower consum |               | r one operation | (/                  |

| Operating<br>Mode                                       | 3.3 V Digital<br>Supply<br>(Vdd3d) | 3.3 V Analog Supply<br>(Vdd3pa, Vdd3a) | 2.5 V Digital<br>Supply<br>(Vdd2d) | 2.5 V Analog<br>Supply (Vdd2a,<br>Vdd2pa) | Total | Unit |

|---------------------------------------------------------|------------------------------------|----------------------------------------|------------------------------------|-------------------------------------------|-------|------|

| Sleep<br>(see Note <sup>[1]</sup> )                     | 0                                  | 0                                      | 0                                  | 6.25                                      | 6.25  | mW   |

| Tx<br>(see Note <sup>[2]</sup> )                        | 9                                  | 345                                    | 8.75                               | 350                                       | 712   | mW   |

| Rx <sub>(max. gain)</sub><br>(see Note <sup>[3]</sup> ) | 9                                  | 47                                     | 8.75                               | 305                                       | 370   | mW   |

[1]Powered-down state; only the CLK40 pads and crystal oscillator are on.

[2] Transmitter and synthesizer are on.

[3] Receiver and synthesizer are on with maximum receive gain.

## 3. Functional Description

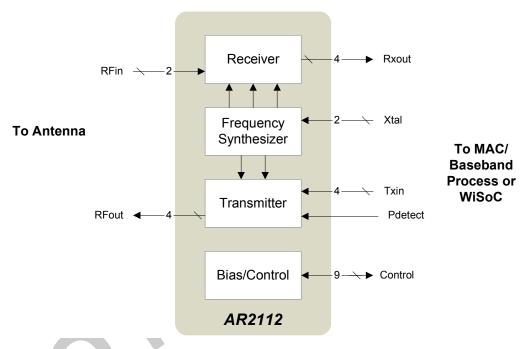

The AR2112 transceiver consists of four major functional blocks:

- Receiver (RX)

- Transmitter (TX)

- Frequency synthesizer (SYNTH)

- Associated bias/control (BIAS)

```

See Figure 3-1.

```

Figure 3-1. AR2112 Functional Block Diagram

### 3.1 Receiver (RX) Block

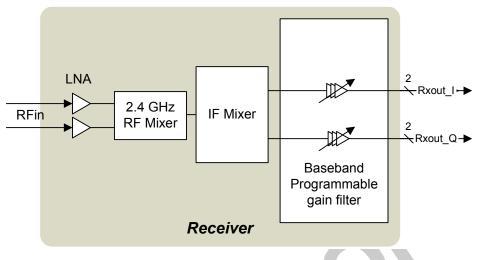

The receiver converts an RF signal (with 20 MHz or 40 MHz bandwidth) to baseband I and Q outputs. The input frequency range of the receiver is 2.4 GHz for IEEE 802.11b/g signals.

The receiver implements an integrated downconversion architecture that eliminates the requirement for an external intermediate frequency filter, while providing the advantages of traditional heterodyne approaches. The receiver topology includes a low noise amplifier (LNA), a radio frequency (RF) mixer, an intermediate frequency (IF) mixer, and a baseband programmable gain amplifier (PGA) as shown in Figure 3-2. The RF mixer converts the output of the on-chip LNA to an intermediate frequency. The IF mixer converts this signal down to baseband I and Q signals. The I and Q signals are low-pass filtered and amplified by a baseband Programmable Gain Filtercontrolled by digital logic. The baseband signals are sent to the ADC of the MAC/Baseband processor or WiSoC. The DC offset of the receive chain is reduced using multiple DACs controlled by the MAC/ Baseband processor or WiSoC. Additionally, the receive chain can be digitally powered down to conserve power.

Figure 3-2. RF Receiver Functional Block Diagram

### 3.2 Transmitter (TX) Block

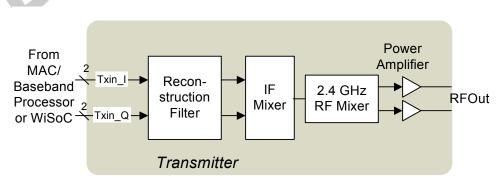

The transmitter converts baseband I and Q inputs to 2.4 GHz RF outputs as shown in Figure 3-3. The inputs of the transmitter are current outputs of the DAC in the AR5212. These currents are low-pass filtered through on-chip reconstruction filter to remove spectral images and out-of-band quantization noise. The I and Q signals are converted to RF signals using an integrated up-conversion architecture. The intermediate frequency (IF) mixer converts the baseband signals to an intermediate frequency. The radio frequency (RF) mixer converts the IF signals into radio frequency signals. These signals are driven off-chip through a power amplifier.

The transmit chain can be digitally powered down to conserve power. To ensure that the FCC limits are observed and output power stays close to the maximum allowed, the transmit output power is adjusted by a closed loop, digitally programmed, control loop at the start of each packet. The closed-loop power control can be based on either an on-chip or offchip power detector. Refer to application notes *External power detection and predistortion* for more details.

Figure 3-3. RF Transmitter Functional Block Diagram

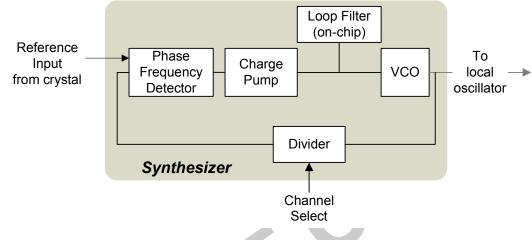

#### 3.3 Synthesizer (SYNTH) Block

The AR2112 supports two on-chip synthesizers to generate local oscillator (LO) frequencies for the receiver and transmitter mixers. Both synthesizers share the topology shown in Figure 3-4. A signal generated from a 40 MHz crystal is used as the reference input for the synthesizer. An on-chip voltage controlled oscillator (VCO) provides the desired LO signal based on a phase/frequency locked loop. The loop filter components are all integrated on chip and can be digitally optimized through the serial interface.

On power up or channel reselection, the synthesizer takes approximately 0.2 ms to settle.

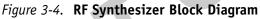

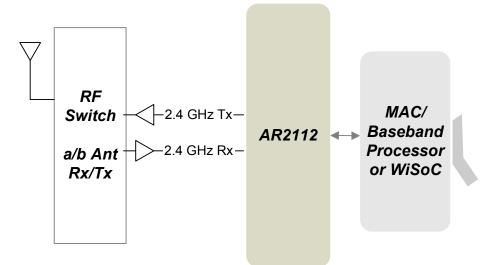

### 3.4 Bias/Control (BIAS) Block

The bias/control block provides the reference voltages and currents for all other circuit blocks (see Figure 3-5). An on-chip bandgap reference circuit provides the needed voltage and current references based on an external 6.19 k $\Omega \pm 1\%$  resistor.

The MAC/Baseband processor or WiSoC controls the state of the AR2112 through the control interface.

## 4. Typical Application

Figure 4-1 shows a typical configuration for a transceiver built with the chip set. This section presents some example filters, diagrams, and component values for reference.

Figure 4-1. Typical Application Block Diagram using the AR2112

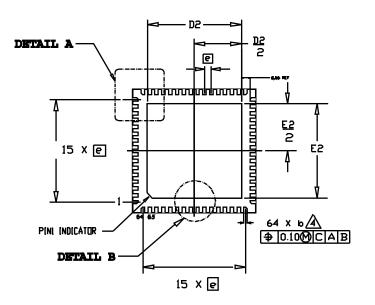

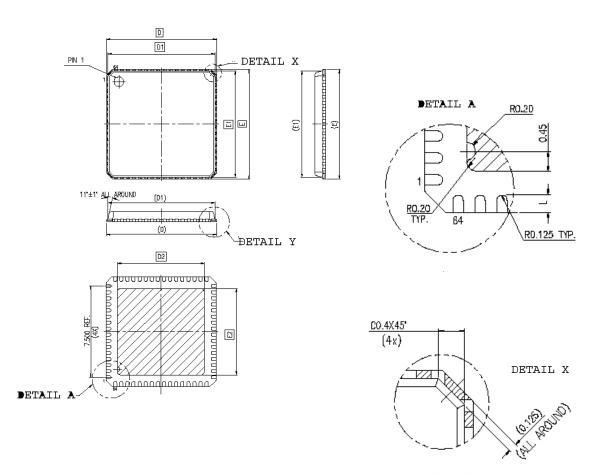

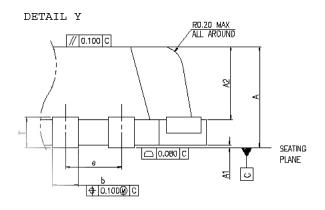

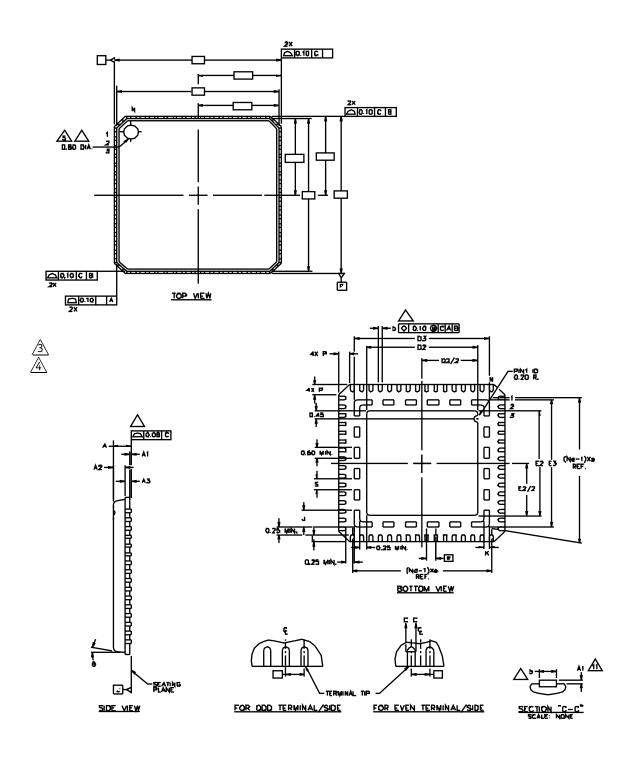

### 5. Package Dimensions

The AR2112 is packaged in a JEDEC MO-220 compliant leadless plastic chip carrier (LPCC). The LPCC can be sourced from any one of three package drawings. The external dimensions are identical from all sources.

The LPCC package drawings and dimensions are provided in Figure 5-1, Figure 5-2, and Figure 5-3, and in Table 5-1.

Figure 5-1. AR2112 "Package A" Dimensions

Figure 5-2. AR2112 "Package B" Dimensions

Figure 5-3. AR2112 "Package C" Dimensions

| Dimension Label | Min. | Nom.      | Max. | Unit. | Description                          |

|-----------------|------|-----------|------|-------|--------------------------------------|

| А               | 0.80 | 0.90      | 1.00 | mm    | Thickness                            |

| A1              | 0    | 0.02      | 0.05 | mm    | Standoff                             |

| A2              | 0.60 | 0.65      | 0.70 | mm    | Cavity Thickness<br>(Package B only) |

| A3              |      | 0.20      |      | mm    |                                      |

| b               | 0.23 | 0.25      | 0.28 | mm    | Lead Width                           |

| D               | 8.90 | 9.00      | 9.10 | mm    | Package Length                       |

| D1              | 8.65 | 8.75      | 8.85 | mm    | Cavity Length<br>(Package B only)    |

| D2              | 6.75 | 6.90      | 7.05 | mm    | Exposed PAD Length                   |

| D3              | 7.15 | 7.30      | 7.45 | mm    |                                      |

| Е               | 8.90 | 9.00      | 9.10 | mm    | Package Width                        |

| E1              | 8.65 | 8.75      | 8.85 | mm    | Cavity Width<br>(Package B only)     |

| E2              | 6.75 | 6.90      | 7.05 | mm    | Exposed PAD Width                    |

| E3              | 7.15 | 7.30      | 7.45 | mm    |                                      |

| e               |      | 0.50 BSC. |      | mm    | Lead Pitch                           |

| L               | 0.30 | 0.40      | 0.50 | mm    | Lead Length                          |

| JEDEC REF       |      | MO-220    |      |       |                                      |

Table 5-1. LPCC "Package A, B, and C" Dimensions

#### Notes:

1 Dimensioning and tolerancing conform to ASME Y14-1994.

2

All dimensions are in millimeters, and all angles are in degrees. The Terminal #1 identifier and terminal numbering convention shall conform to JESD 95-1 and SPP-012. 3 Terminal #1 identifier L is located within the zone indicated. It may be either a mold or a marked feature.

4 Dimension b applies to metallized terminal and is measured from the terminal tip.

### Ordering Information

The order number is determined by the selection of these options. See the following example.

## **Revision History**

| Revision       | Description of Changes                                                        |

|----------------|-------------------------------------------------------------------------------|

| April 2003     | Initial draft                                                                 |

| June 2003      | Updated Electrical Characteristics.                                           |

| September 2003 | Updated Electrical Characteristics.                                           |

| October 2003   | Added "Package B" and updated Table 5-1, "LPCC 'Package A and B' Dimensions". |

| March 2004     | Upadated Package 'A, B, and C' Dimensions. Updated tcase temperature.         |

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Atheros assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any updates. Atheros reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.

Document Number: 981-00018-003

A T H E R O S<sup>®</sup>

COMMUNICATIONS

**Incorporated** 529 Almanor Avenue Sunnyvale, CA 94086 t: 408/773-5200 f: 408/773-9940 www.atheros.com

**Atheros Communications**